本文是一篇电力论文,电力系统的出现,使用高效、无污染、使用方便、易于控制的电能得到广泛应用,推动了社会生产各个领域的变化,开创了电力时代,发生了第二次技术革命。电力系统的规模和技术高低已成为一个国家经济发展水平的标志之一。(以上内容来自百度百科)今天为大家推荐一篇电力论文,供大家参考。

第一章 绪论

1.1 引言

音频功率放大器,简称“音频功放”。它应用在音频功放系统中,对音频信号起着放大的作用。1906 年,DeForest 发明了世界上第一台音频功率放大器[1],接着陆续出现了 A 类音频功率放大器、B 类音频功率放大器、AB 类音频功率放大器、D 类音频功率放大器、G 类音频功率放大器、和 H 类音频功率放大器[2]。A 类音频放大器,也称为甲类音频放大器,因为晶体管始终工作在线性范围内,故瞬态失真和交越失真小,放大器的效率理论上的最大值只有 25%。B 类音频放大器也称为乙类音频放大器,由于输出晶体管的导通时间只有半个周期,与 A 类音频放大器相比,存在交越失真,线性度较差。AB 类音频放大器,也称为甲乙类音频放大器,在 A,B 类音频放大器的基础上进行了一些改进,输出晶体管导通时间大于输入信号半个周期,而又小于输入信号整个周期,线性度和电源效率介于 A 级和 B 级之间。D 类音频功率放大器,有时也称为数字功放,是通过控制开关单元的 ON/OFF,来驱动扬声器,也称为开关放大器。具有效率高的突出优点,理论效率为 100%,实际效率可达到 85%。但在开关调制的过程中会引入非线性误差,失真较大。G 类放大器的主要特点是具有高低压电源,当输入信号电压幅度大于晶体管的阈值电压时,晶体管采用高压电源供电;当输入信号电压幅度小于晶体管的阈值电压时,晶体管采用低压电源供电,从而降低功耗并提高功率效率。H 类音频功率放大器与 G 类音频功率放大器类似,其与 G 类音频功放的主要区别在于,它使用动态电源电压的方式给晶体管供电,而非采用从一组电源直接切换到另外一种电源的方式,这种方式会带来功耗的降低。由以上可以得到,D 类音频功放是所有音频功放类别中电源效率最高的,满足现今追求的低碳环保、高效节能的理念。随着时代的发展,如今的视听产品越来越向着小型化,便携式的发展,低功耗产品的设计已经是大势所趋。所以具有高功率效率的D 类音频放大器越来越受到人们的关注,成为近年来研究的热点。

...........

1.2 研究背景及意义

早在 1938 年,有人就发明了应用于 D 类音频放大器的脉宽调制(Pulse WidthModulation,PWM)技术[3],但由于音频放大器是使用的是电子管,所以开关特性较差,不能实现高的电源效率。由于在 1947 年美国贝尔实验室发明了世界上第一个晶体管[4],D 类音频放大器的概念和工作原理采正式被提出来[5]。直到 1964 年,第一个商用 D 类音频放大器 X-10 在英国公开面世,X-10 由 Sinclair Radionics 的 Eden 和Westwood 设计并制造,但它工作却不太稳定[6]。接下来,SinclairRadionics 公司又推出了 X-20 系列,X-20 虽然输出功率高达 20W,但符合功率要求的锗双极性晶体管开关速度太慢,达不到开关频率的要求,从而会影响 X-20 的性能。在 1974 年,InfinitySystems 公司推出了第一台输出功率大于 100W 的 D 类音频放大器,后来推出了更高功率的 D 类音频放大器,但由于硅双极晶体管的可靠性差异很大,导致功率放大器声音质量一直不太理想,最终,InfinitySystems 公司放弃了 D 类音频放大器的设计和生产。D 类音频放大器黯淡的市场局面直到 20 世纪 80 年代才逐渐改变,由于场效应晶体管的迅速发展,D 类音频放大器才开始得到更多的关注,很多公司投入了大量的经费去重新研究 D 类音频功率放大器。如今,许多国际知名的半导体公司,如恩智浦(NXP)、意法(ST)和德州仪器(TI)等都有自己的产品,D 类音频放大器已广泛应用于通信、娱乐、助听、教育等相关领域。

..........

第二章 数字 D 类音频功率放大器的结构

数字 D 类音频功率放大器通过采样算法调制将数字信号调制成脉冲宽度信号(PWM),然后将调制后的开关信号驱动功率晶体管,实现信号的放大,最后通过低通滤波器,滤除高次谐波,实现音频信号的放大。简单来说,数字 D 类放大器系统包括调制器和功率输出级。对于调制方法本章主要讲述了 PWM 调制原理和 PDM 调制原理。对于功率输出级,本章给出了其基本结构,最后给出了评价 D 类音频功率放大器的评价标准,包括:功率输出级的谐波失真、功率、电源效率和 EMI 等等。

2.1 D 类放大器的调制方法

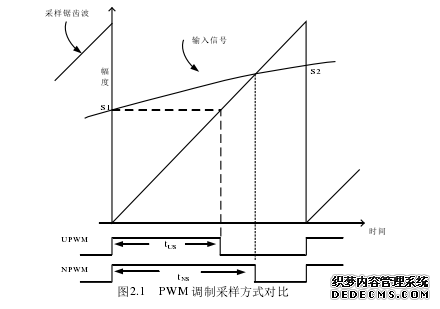

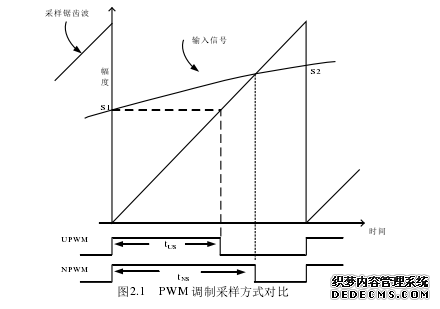

数字 D 类音频功率放大器的调制方法主要包括两种,脉冲密度调制(PDM)和脉冲宽度调制(PWM)。PDM 产生密集度不等的脉冲信号,这种密集程度和输入信号的幅值相对应,而 PWM 输出的脉冲信号宽度与输入信号的幅值相对应。比较器输出 PWM 的原理是这样的,当输入信号的幅度小于载波幅度时,比较器输出为低电平“0”;当输入信号的幅度大于载波幅度时,比较器输入为高电平“1”,这样就可以得到脉冲宽度随着输入信号的幅度变化而变化的 PWM 信号。在 PWM 调制过程中,输入信号与采样锯齿波斜边的交点位置决定。作为自然采样过程,公式(2-1)可以有如下阐述。第一项 K 是 PWM 输出信号的直流分量,和公式后面几项具有独立性。第二项表示输入的音频调制信号,第三项代表载波信号和与载波信号相关的谐波,可以通过低通滤波器过滤掉。最后一项代表调制信号和它的交调失真,这个交调失真是由载波和其谐波失真产生,通常情况下,这些可以被忽略掉。由公式(2-1)第二项可以看到,调制过程中输入信号被精确地保留下来,没有谐波分量产生,因此理论上 NPWM 调制不会产生谐波失真。

............

2.2 功率输出级

如图(2-5)所示是 D 类放大器的输出级原理框图,功率输出级电路用来放大 PWM信号和通过低通滤波器将放大后的 PWM 信号中的高频次谐波过滤掉,从而还原出干净的原输入音频信号。图 2-5 只是一个简化的功率输出级电路图,在实际应用中,还需要加入驱动元件,以增强 PWM 信号的驱动能力。通常在低压情况下,我们使用全桥电路,可以得到双倍的输出电压摆幅和 4 倍的输出功率,而半桥电路的设计需要双电源,优点是可以节省元器件。在实际电路测试中,由于开关晶体管的开关行为并不是理想的,PWM 信号上升沿、下降沿也有一定的延迟现象,这些会带来一定的失真和非线性,这些噪声会直接耦合到输出端,增加输出级信号的谐波失真。同时电源信号很容易受到干扰,可以在电源两端加上去耦电容,此电容可以为系统提供较稳定的电源,同时可以减少其他元件受此电源噪声的影响。

...........

第三章 基于 C-LAG-NR 算法调制原理及实现方法........17

3.1 常见的采样算法........17

3.2 基于 C-LAG-NR 的采样算法........ 21

3.3 本章小结 26第四章 基于 FPGA 的数字音频放大器系统的设计与仿真........ 27

4.1 数字 D 类音频放大器系统的结构........ 27

4.2 数字音频放大器系统的系统仿真........ 27

4.3 C-LAG-NR 采样算法硬件实现与仿真........ 31

4.4 功率输出级电路设计与仿真........ 34

4.5 本章小结........ 37

第五章 基于 FPGA 的数字音频放大器系统的测试与分析........ 39

5.1 测试平台总体结构介绍........ 39

5.2 功率输出级 PCB 设计........ 39

5.3 D 类音频功放开关放大器测试........ 42

5.4 D 类音频功率放大器的效率测试........ 49

5.5 本章小结........ 50

第五章 基于 FPGA 的数字音频放大器系统的测试与分析

第四章对 C-LAG-NR 采样算法进行了系统级仿真和硬件电路的实现,接下来搭建 D 类音频功放系统的测试平台,测试基于 C-LAG-NR 采样算法的 D 类音频功放系统性能,并分析测试结果。

5.1 测试平台总体结构介绍

如图(5-1)所示为 D 类音频功率放大器的测试平台,首先由信号源产生20Hz~20kHz 正弦波,通过 ADC 模数转化器把模拟的信号转换成为数字信号,然后再通过用 FPGA 实现的调制器对数字信号进行调制从而得到 PWM,连接功率放大器和滤波电路,最终还原出原输入信号的波形。通过示波器测量扬声器两端的电压信号,并对信号进行 FFT 分析。D 类音频功放系统功率输出级电路包括开关放大器和滤波器组成。在第四章中,已经对功率输出级电路进行仿真,按照仿真电路图对功率输出级进行 PCB 板级电路的设计,包括 PCB 原理图和 PCB 版图的设计。图(5-3)是功率输出级电路的 PBC 版图,包括开关放大电路和滤波电路。此版图经过前两次的制版测试失败之后做了一些调整,因为这是关于 D 类音频功放的 PCB版图,所以对版图的布局要求较高,PCB 布局要求如下:1,LC 滤波器中 L 和 C 之间的连线要尽量短,以降低寄生电感,降低对谐振频率的影响;2,芯片与功率管要尽量靠近,以增强芯片对晶体管的驱动能力;3,去耦电容要加在电源两端,与功率晶体管靠近,发挥去耦电容作用;4,尽量增加功率部分连线的线宽,使其能够通过较大电流同时减小导线的电阻;5,PCB 的走线要横平竖直,PCB 板顶层和底层的走线要尽量垂直,减少信号之间的干扰;6,走线的距离应尽量短,减少因走线增加系统的寄生电阻、寄生电容等,影响设备的性能。#p#分页标题#e#

........

总结

随着信息技术的日新月异和应用需求的不断发展,现代音频系统不断朝着多功能、高音质、小体积、低功耗、高效率等方向发展。迷你音响系统、机顶盒、个人电脑、LCD 电视、移动电话等消费类产品不断涌向人们的生活。这些繁荣景象的出现有数字功率放大器的一份功劳,同时也促进数字功放的发展。数字 D 类功放具有高效率、低功耗的优势,但也存在谐波失真较大的缺陷,本文致力于数字 D 类功放调制算法的研究,力争为提高数字 D 类功放电源效率和减小谐波失真贡献自己的一份力量。现在对本文所做的主要工作总结如下:

(1)对已有的 D 类功放调制算法进行研究与分析,在此基础上提出基于三阶拉格朗日插值方法的 C-LAG-NR 的采样算法,提高了采样算法的精度并有效降低 D 类功放的谐波失真。

(2)在 Matlab 软件中建立 D 类功放系统模型,对 C-LAG-NR 采样算法以及其他采样算法进行系统仿真。将所提出算法与已有算法的谐波校正性能进行比较,进一步完善和提高该算法的有效性。

(3)设计基于 C-LAG-NR 采样算法的硬件电路,并将 Verilog 代码的烧写 FPGA开发板中;设计功率放大模块和滤波电路模块的 PCB 版图并制版,并完成 PCB 电路板的调试与优化。

(4)搭建基于 C-LAG-NR 采样算法的 D 类音频功放的测试平台,完成 D 类放大器的测试,测试结果表明,D 类音频功放的效率为 80%左右,满足 D 类放大器的要求,且该放大器能够对原输入的音频信号进行正确的还原。

..........

参考文献(略)